近年來,隨著高速數字化通訊時代的到來,各行業高速信號軟、硬體快速發展,使其工作的頻率與頻寬越來越高,所以整體對連接器元件的性能要求也更加嚴苛,再加上連接器件小型化的設計趨勢,連接器在信號傳輸完整性上面臨很大的挑戰。

一、高速連接器信號完整性的基礎理論

在整體機構縮小化及高頻化的條件下,將會引發的信號完整性的問題需要引起特別重視,如特性阻抗(Impedance)、插入損耗(Insertion Loss)、返回損耗(Return Loss)、串擾(Crosstalk)等,其中又以特性阻抗及串擾對連接器的訊號完整性影響最大。

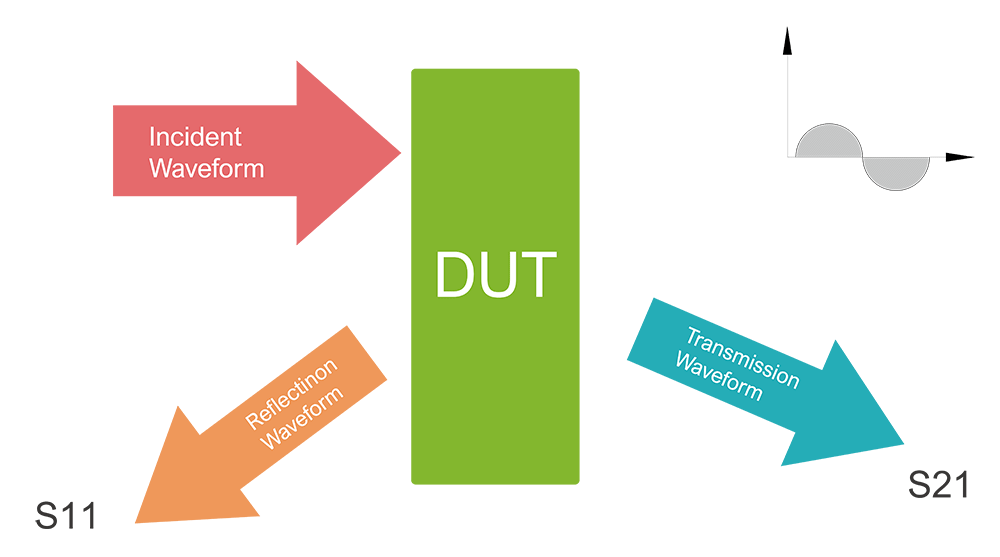

在信號完整性上通常使用S參數(Scattering-parameter)作為描述互連的寬帶高頻行為的標準格式。 S參數是描述標準波形如何從互連或被測元件散射出去的一種格式。

圖 1: 標準波形輸入DUT散射情況, 傳輸波形S21表示插入損耗(Insertion Loss),反射波形S11表示返回損耗(Return Loss).

圖 1: 標準波形輸入DUT散射情況, 傳輸波形S21表示插入損耗(Insertion Loss),反射波形S11表示返回損耗(Return Loss).二、影響高速連接器信號完整性的關鍵因素

通常,影響高速連接器的信號完整性的因素有:設計空間、傳輸速率、信號損耗等。而不同的PCB Layout設計跟這些因素息息相關,從而對整體信號完整性起著關鍵性的影響。在不同的PCB Layout設計下,連接器所呈現出的高頻特性都會有所差異。

目前,標準高速連接器已有完整的架構及規範來依循,工程師更多只需在該架構下對設計進行調整來滿足規範要求的高頻條件即可,若是客制化的產品,需求則不同。 Greenconn在高速連接器的開發上一直以定制化為主,一般情況下客戶只會提供設計空間、所需的傳輸速率,很多時候甚至對信號損耗的要求不確定,這就需要針對不同的PCB Layout反複調整設計方案。因此,工程師往往會藉助FEA模擬來輔助高速連接器設計,確保信號完整性。

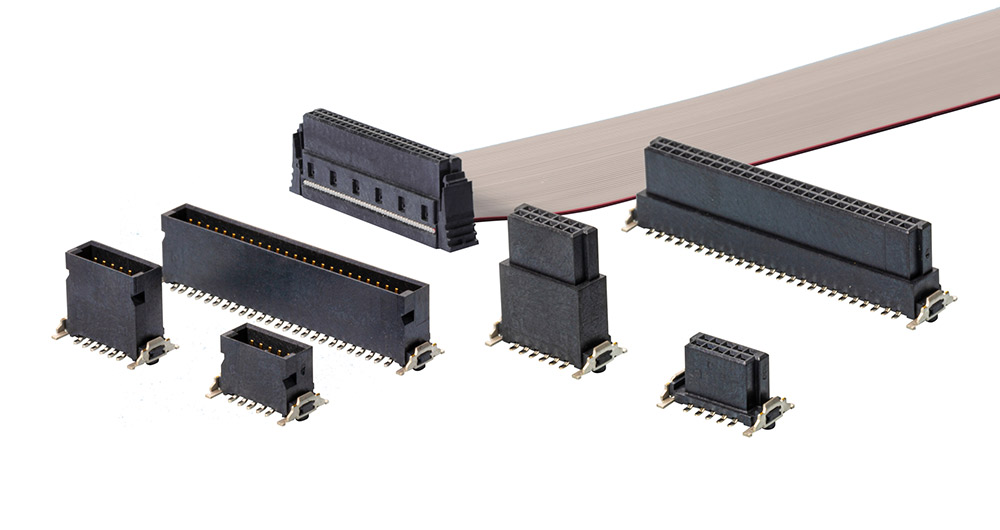

圖2: Greenconn 1.27mm高速闆對板和線對板連接器採用雙觸點彈簧端子設計,具有高抗震性,信號傳輸速率高達4GBits

圖2: Greenconn 1.27mm高速闆對板和線對板連接器採用雙觸點彈簧端子設計,具有高抗震性,信號傳輸速率高達4GBits三、FEA模擬如何輔助高速連接器設計

Greenconn在高速連接器的客制化開發中,通過應力及高頻FEA模擬不斷調整機構設計以滿足客戶需求,最終將產品的高頻特性實測與模擬的進行對比,確認其模擬的有效性,並多次對比以累積經驗,持續提升模擬的確確性。具體分為如下幾步:

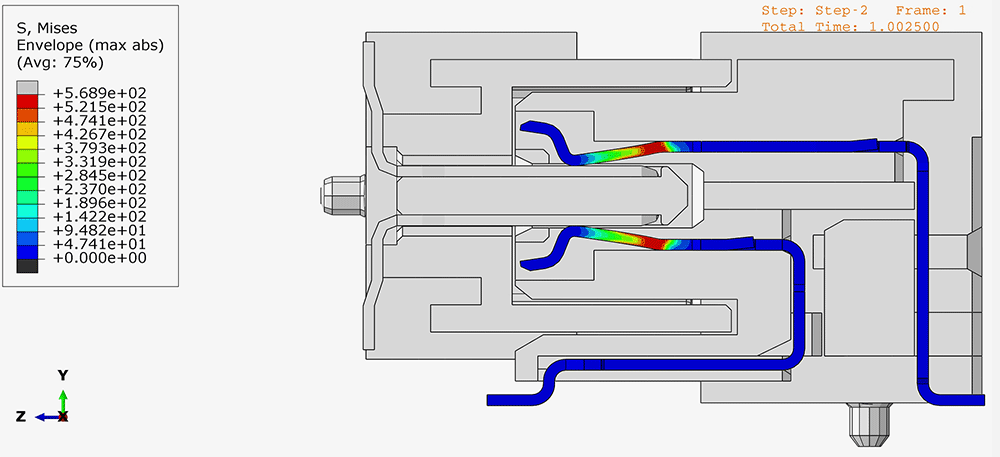

- 通過FEA插拔模擬後可得到該連接器的插拔力數據,從而判斷該機構設計是否符合需求,並且可從FEA的模擬結果中導出連接器對插之後端子的變形狀態。經過多次的驗證得知,只要材料的參數及FEA模擬的條件設定正確,其得出的插拔力結果及端子的變形狀態非常接近實際值。

圖 3: Greenconn通過多次高速連接器FEA插拔模擬,獲取接近實際的插拔力數據及端子的應變狀態。

圖 3: Greenconn通過多次高速連接器FEA插拔模擬,獲取接近實際的插拔力數據及端子的應變狀態。 - 將FEA模擬導出的端子變形狀態加上PCB重新繪製3D模型,將繪製好的模型導入到高頻FEA軟件中,並對模型進行參數設置以及給予訊號後即可進行高頻模擬。

- 通過不斷反覆的調整設計及模擬之後,獲得符合客戶所需求的S參數。四項高頻條件分別為特性阻抗(Impedance)、插入損耗(Insertion Loss)、返回損耗(Return Loss)、近端和遠端串擾(NEXT and FEXT)。

隨著傳輸的時鐘頻率越高所產生的信號完整性問題就越嚴重,對連接器的設計考驗也就越嚴苛。在高頻原理上,特性阻抗越匹配就越能減少信號完整性問題的發生,但在空間機構的限制下會使連接器接觸端子的形狀越不規則,導致連接器要匹配到高頻傳輸的特性阻抗難度較大,尤其PCB Layout的設計對信號完整性的影響很大。因此,客制化的高速連接器的開發,通過借助FEA模擬可以獲得更精準參考,以保障信號完整性,滿足設備所需的高速傳輸要求,並有效避免資源浪費,節省成本。